Program Timetable

|

Day1

Thursday 13th June |

|

|

Time |

Program |

|

08:50 - 09:00 |

Opening |

|

09:00 - 10:00 |

Keynote lecture 1

Highly Efficient Designs: Art, Magic or Engineering? |

|

10:00 - 10:30 |

Coffee/Tea Break |

|

10:30 - 12:10 |

Session 1: Best paper candidates

(1) Accelerating Sequential Monte Carlo Method for Real-time

Air Traffic Management

(2) NCBI BLASTP on the Convey HC1EX

(3) Efficient Custom Computing of Fully-Streamed Lattice

Boltzmann Method on Tightly-Coupled FPGA Cluster

(4) A Hybrid CPU-FPGA System for High Throughput (10Gb/s)

Streaming Document Classification |

|

12:10 - 14:00 |

Session 2: Solarflare Luncheon Session

In this session, Solarflare will give a presentation on

their University Program, followed by Q&A and one-to-one

discussions. |

|

14:00 - 14:50 |

Session 3: Applications

(5) Customisable Pipelined Engine for Intensity Evaluation

in Multivariate Hawkes Point Processes

(6)

Accelerating Finite Difference Time Domain Simulations with

Reconfigurable Dataflow Computers |

|

14:50 - 16:20 |

Session 4: Poster Presentation

(P1) Deadlock-Free

Routing Strategy for Stacking 3-D NoCs with Different

Topologies

Daisuke Sasaki, Hiroki Matsutani, Michihiro Koibuchi

and Hideharu Amano

(P2) An Energy

Effective SIMD Accelerator for Visual Pattern Matching

Calin Bira, Liviu Gugu, Radu Hobincu, Valeriu

Codreanu, Lucian Petrica and Sorin Cotofana

(P3) A 7-depth search

FPGA Connect6 Solver

Retsu Moriwaki, Takashi Yoza, Yuki Kamikubo, Yuki

Torigai, Akira Tanigawa, Takayuki Kubota, Hiroyuki Ito, Yuya

Shirahashi and Minoru Watanabe

(P4) High Performance

Gapped BLAST with the Two-hit Method Implementation on FPGA

Mohd Nazrin Md Isa, Khaled Benkrid and Thomas Clayton

(P5) Cache-aware

Parallel Programming for Manycore Processors

Ashkan Tousimojarad and Wim Vanderbauwhede

(P6) Intensity and

Distance Thresholding in Hardware to Enable Flexible Blob

Detection for a Vision System with Limited Bandwidth

Peter Samarin, Timur Saitov, Rainer Herpers and

Kenneth Kent |

|

16:20 - 17:10 |

Session 5: High-level-language reconfigurable systems

(7) A reconfigurable

Java accelerator with software compatibility for embedded

systems

(8) Reconfigurable

and Hardwired ORB Engine by Java-to-HDL Synthesizer for

Realtime Application |

|

19:00 |

Banquet at City Chambers (253 High Street, Edinburgh, EH1

1YJ)

City Chambers is a fantastic historic building founded in

1761 and now used as the home of the City of Edinburgh

Council, in Scotland.

All registered attendees are welcome to join this banquet;

costs have been included in the registration fee. |

|

|

|

|

Day2

Friday 14th June |

|

|

Time |

Program |

|

09:00 - 10:00 |

Keynote lecture 2

Execution time should be as short as possible, but not

shorter |

|

10:00 - 11:30 |

Session 6: Poster Presentation

(P7) Granularity Problem of Runtime Reconfigurable Design

Flows

Dominik Meyer and Bernd Klauer

(P8) A Fast Runtime Visualization Framework for Efficient

Development of Scientific Applications on CUDA

Kota Aoki, Keisuke Dohi, Yuichiro Shibata and Kiyoshi

Oguri

(P9) Low Memory Logarithmic Converter

Syed Ahmed,

Srinivas M.B, Pavan Sastry and Sreehari V. A

(P10) High Accuracy CMASOTB/LPT-3: The first prototype chip

of Cool Mega Array on Silicon On Thin BOX

Hongliang Su, Weihan Wang, Kuniaki Kitamori and

Hideharu Amano

(P11) A dependability-increasing demonstration for a

16-configuration context optically reconfigurable gate array

Akira Tanigawa and Minoru Watanabe

(P12) Chebyshev Polynomial Smoother in Multiple GPU-based

AMG Method

Yuki Araya, Akihiro Fujii and Teruo Tanaka |

|

11:30 - 12:20 |

Session 7: Numeric operation

(9) Fixed-Point Trigonometric Functions on FPGAs

(10) Performance Evaluation of 3-D Stacked 32-bit Parallel

Multipliers |

|

12:20 - 14:00 |

Lunch

Break |

|

14:00 - 14:50 |

Session 8: Architecture

(11) The Ultrasmall

Soft Processor

(12) Customisable

Architectures for the Set Covering Problem |

|

14:50 - 15:20 |

Coffee/Tea Break |

|

15:20 - 16:10 |

Session 9: Reconfigurable SoCs

(13) Blueshell: A Platform for Rapid Prototyping of

Multiprocessor NoCs and Accelerators

(14) A Run-time Reconfigurable System for Adaptive High

Performance Efficient Computing |

|

16:10 - 16:40 |

Closing & Award Ceremony |

|

|

|

|

Notes:

- Each regular paper has a 20-minutes full-time speech and a

5-minute discussion.

- Each poster paper has a 5-minute short-time speech and

1-hour poster presentation.

- The best paper award will be judged by HEART2013 Program

Committee in the session of the best paper candidates

- The best poster award is selected from all presentations.

- HEART2013 award ceremony will be held in the closing talk.

- The no‐show regular paper will not be invited to ACM CAN.

- The size of the poster could be as large as A0 (1189 x 841

mm), portrait orientation. |

|

Download program timetable in PDF here

Banquet at City Chambers

A banquet will be held on:

13th June 19:00pm--22:30pm (the first day of the

conference)

at City Chambers, 253 High Street, Edinburgh, EH1 1YJ

City Chambers is a fantastic historic building founded in 1761 and

now used as the home of the City

of Edinburgh Council, in Scotland.

All registered attendees are welcome to join this banquet, costs

have been included in the registration fee.

We suggest all attendees arrive at 19:00pm, as the dinner will start

at 19:30pm.

More details about this building can be found at City

Chamber Wikipedia..

Map of City Chambers:

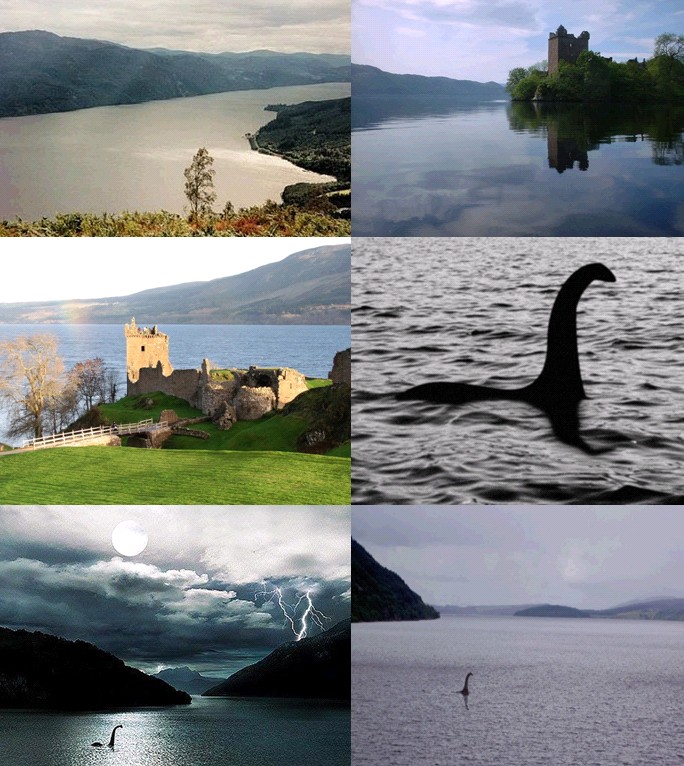

One-day tour to Loch Ness

A one-day tour will be

available on:

15th June 08:00am--20:30pm (the third day of the

conference)

departure from High Street, Royal Mile, Edinburgh

The tour cost about £50 depending on the number of

delegates, a private bus will be booked only for our conference. The

tour is optional and the price NOT included in the registration fee.

The tour invites you to mysterious Loch Ness, with an option to

visit Urquhart Castle and take a boat cruise on this legendary

stretch of water. It covers a variety of sites including Loch Ness,

Urquhart Castle, Fort William, and Spean Bridge. More information

can be found

here.

Loch Ness is a large, deep, freshwater loch in the Scottish

Highlands, which is best known for its mysterious monster

"Nessie". The Nessie is the most controversial creature in the

world, and a number of news and pictures have been reported.

More details about this loch and the monster can be found at

Loch Ness Wikipedia and

Loch Ness

Monster .

Departure place:

View Larger Map

News

+

HEART2014 will be held in

Sendai, Japan

9th -11th, June, 2014.

WEB page will be available soon

at http://www.isheart.org

+ HEART2013 Keynote Speakers:

-

Mr. Ken Chapman

Xilinx Inc.

+ Selected accepted papers at

HEART 2013 will be included in

post-proceedings of

Special Issue on ACM SIGARCH

Computer

Architecture News

(CAN)

+ HEART2013 Sponsors: